Acute逻辑分析仪 Serial VID 技術文章

在 Intel 平台中, 電源管理(Power Management Integrated Circuit, PMIC)通訊協定從 VR12 開始一改過去以 Parallel 傳輸模式, 調整為 Serial 傳輸.SVID使用 3 條控制線路 (Clock, VDIO, Alert) 來進行資料傳輸. SVID 的基本傳輸概念, 就是由 CPU 發送命令給真正負責電源輸出控制的 VR 控制器(Controller) IC, 然後在 VR 控制器準備好所設定的電壓之後會以 Alert 訊號通知 CPU, 來達成一個完整的命令流程. 因此, 當 SVID 通訊過程中發生的任何問題, 多半會立即的引起整個系統電源的不正確, 而造成某些關鍵零組件停擺而使的系統當機無法使用.

為此, 在 SVID 除錯的過程中, 會採行邏輯分析儀與示波器搭配的做法來進行. 會使用這兩種儀器搭配的優勢是

1. 邏輯分析儀

SVID 工作電壓Vtt=1.0-1.1V, Clock 速度約 26.25MHz, 因此要能擷取 SVID

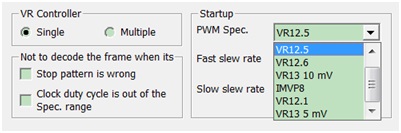

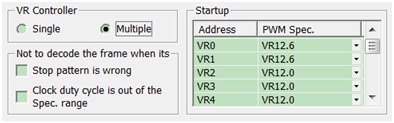

訊號的邏輯分析儀必須要有較佳的電壓靈敏度及足夠的採樣頻率, 才能進行完善的訊號擷取.然後, 搭配具備完善 SVID 通訊協定分析 (Bus Decode), 來進行數位訊號分析與解碼.本文將會以皇晶科技邏輯分析儀做為量測說明之設備, 其已支援 VR12 (IMVP7), VR13, IMVP8 等 SVID 最新規範.同時也支援 Single VR(圖一) 與 Multi VR (圖二)模式的分析.

圖一

圖二

2. 示波器

圖三

圖三

例舉2個量測應用案例, 並分析可能的問題原因

1. SVID匯流排訊號品質不良問題:

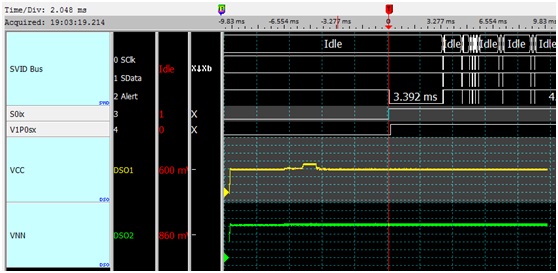

其問題癥狀為系統突然當機, 此時用示波器檢查 SVID 匯流排, 已經沒有任何訊號在傳送, 經使用邏輯分析儀逾時觸發與轉態儲存功能, 定位到 SVID 匯流排在停止發送訊號前, 最後所下的命令.

在圖四中, Alert 訊號是從 VR 控制器回傳VRSettled訊號給 CPU, 但出現了 VDIO 與 Alert線路間發生串音(Crosstalk)現象. VDIO 的訊號跳到 Alert 訊號線上, 造成 SVID 匯流排錯誤而使系統當機.此類問題的解決法, 就是檢視 PCB 線路布局或搭配示波器查看, 找出可能引起訊號反射或串音之問題點.

圖四

1. VR 控制器回應 Alert過慢

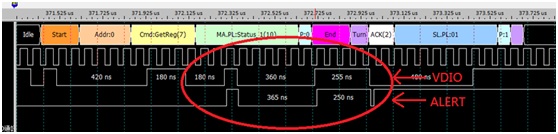

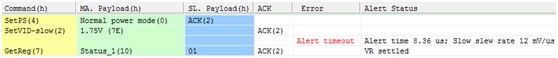

隨著 SVID 版本使用不同命令(SetVID-Fast, SetVID-Slow)時, 在命令發出之後 VR 控制器必須根據所設定之電壓差, 在規定的時間內(Slew rate)完成工作並往 CPU 送出 Alert 通知. 若Slew rate發生逾時(Time-out), 可能會有不可預期的問題發生.圖五說明了, 以 SVID SetVID-Slow 的時候, 發現其 Slew rate 超過預期的時間所提出的 Alert Timeout警告訊息. 此類問題的解決法可能偏向於 VR 控制器, 是否 VR 控制器在這樣的電壓差調整時, 其 Alert Slew rate 不符合規格.

圖五

從上述兩個案例可以看出, 邏輯分析儀在 SVID 問題檢查時, 可有效的快速協助訊號定位, 並立即可根據解碼結果來做問題的釐清,大幅的縮小查問題的範圍. 若需會同其他部門或IC供應商作問題討論的時候, 也可以因為有數位與類比訊號波形而縮短溝通時間.

總而言之, 隨著 Intel 在手持式系統的布局, 使 PMIC 功能面的複雜度提高,量測 SVID 匯流排時混合使用數位與類比儀器成為必要的組合. 尤其在觀察匯流排行為的時候, 能根據 SVID 不同版本將 PWM Table或 Slew rate來做詳盡的解碼, 將有助於更快的釐清問題.