Acute逻辑分析仪 皇晶LA&PG產品應用060324

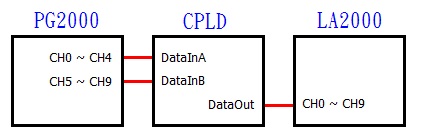

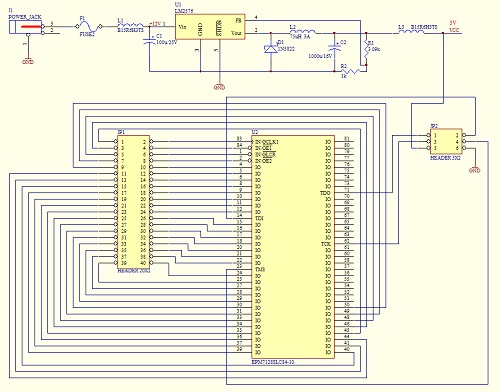

Acute logic analyzer (LA2000P series or PkLA1000 series) and programmable data generator (PG2000 series or PkPG2000 series) can be used as verification tools to Altera CPLD multiplexer. In order to conduct this application, there are three devices needed: one LA2000P logic analyzer, one PG2000 programmable data generator, and one Altera EPM7128S evaluation board which MUST have a EPM7128S chip with its power and ground connected to the evaluation board’s power and ground. The EPM7128S chip’s I/Os are all connected to the evaluation board’s Pin Header in order to connect the LA2000 with the PG2000. The circuits look like:

Use Altera development software to encode the source code of the EMP7128S CPLD and write into the CPLD in JTAG (JP2).

Source code (AHDL) for the EMP7128S CPLD:

INCLUDE "LPM_MULT.inc";

SUBDESIGN MyMul

(

DataInA[4..0] : INPUT;

DataInB[4..0] : INPUT;

DataOut[9..0] : OUTPUT;

)

VARIABLE

Mul :LPM_MULT with( LPM_WIDTHA = 5, LPM_WIDTHB = 5,

LPM_WIDTHS = 5, LPM_WIDTHP = 10 );

BEGIN

Mul.dataa[] = DataInA[];

Mul.datab[] = DataInB[];

DataOut[] = Mul.result[];

END;

Connect Channel 0-9 of the LA2000P to Pin Header of JP1 (DataOut[9..0] defined in EPM7128S), connect Channel 0-9 of the PG2000 to Pin Header of JP1 (DataInA[4..0] and DataInB[4..0] defined in EPM7128S).